-

Type:

Task

-

Resolution: Unresolved

-

Priority:

Major

-

Component/s: None

-

None

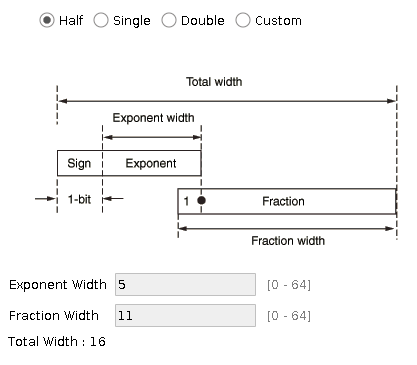

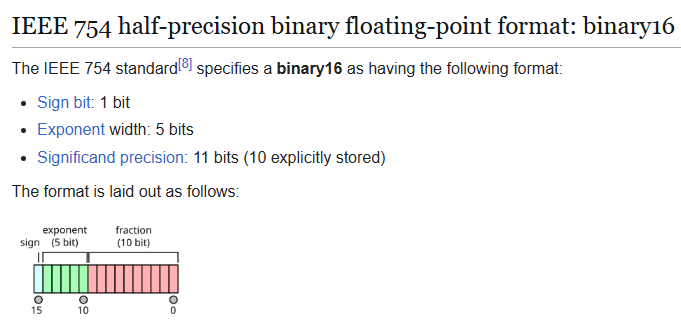

IEEE definition is a "1-5-10" bit layout:

NVIDIA CUDA is also"1-5-10" bit layout:

This structure implements the datatype for storing half-precision floating-point numbers. The structure implements assignment, arithmetic and comparison operators, and type conversions. 16 bits are being used in total: 1 sign bit, 5 bits for the exponent, and the significand is being stored in 10 bits. The total precision is 11 bits. There are 15361 representable numbers within the interval [0.0, 1.0], endpoints included. On average we have log10(2**11) ~ 3.311 decimal digits.

https://docs.nvidia.com/cuda/cuda-math-api/cuda_math_api/struct____half.html

AMD/Xilinx is also a "1-5-10" bit layout: